This is a cryptography accelerator chip for the Skywater MPW-THREE tapeout. It includes an AES256 core (with some key-entropy restrictions to reduce the number of bits in the key), a SHA256 core, a VGA game demo, and some other experimental structures. This includes improved versions of the unsuccessful cores from MPW-ONE.

For documentation on the AES and SHA cores (including the original Chisel source code), see asinghani/crypto-accelerator

This chip contains 4 major components:

-

AES128/256 Accelerator

- Optimized for balance between speed and area, can encrypt or decrypt a 16-byte block in ~20 cycles for AES128 or ~28 cycles for AES256

- Supports both ECB and CBC modes (CBC is recommended because it is much more secure against certain types of attacks) with no performance penalty for using CBC

- Has some internal key-entropy limitations since it is meant for experimental use

-

SHA256 Accelerator

- Can hash a single 512-bit block in ~66 cycles (and is able to process multiple blocks immediately back-to-back, i.e. when hashing a large file)

-

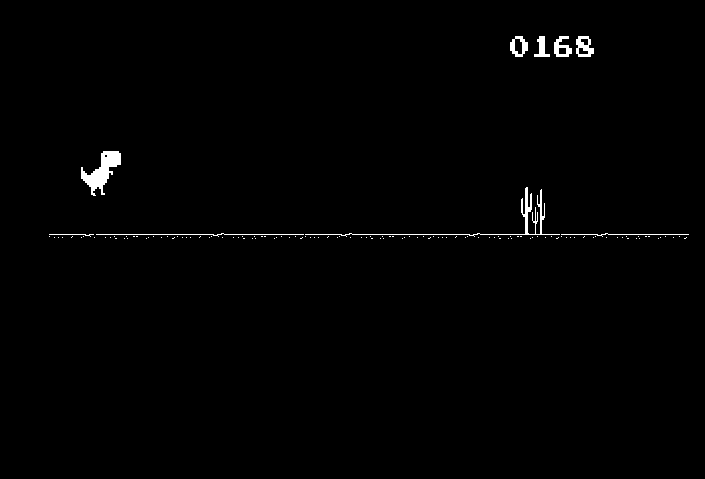

VGA Game Demo

- Contributed by Ethan Polcyn (and then ported to run on the ASIC environment)

- Consists of a small infinite side-scrolling jumping game (based on the Chromium Browser's "No internet"-game), playable using button input from one of the chip's I/O pins

- Renders VGA video output at 640x480 through the chip's output pins

- Caravel harness/padframe

- Contains a picorv32 CPU (which is used to interface with the rest of the cores through the Wishbone bus) and the padframe

- See efabless/caravel for details.